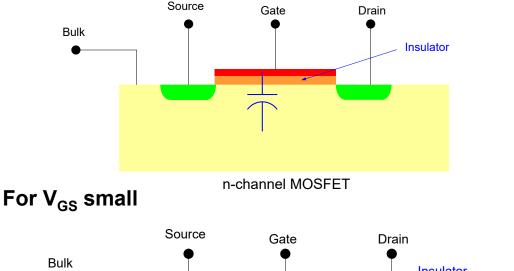

#### EE 330 Spring 2024 Rm 1011 Coover

### EE 330 Lecture 7

**Propagation Delay**

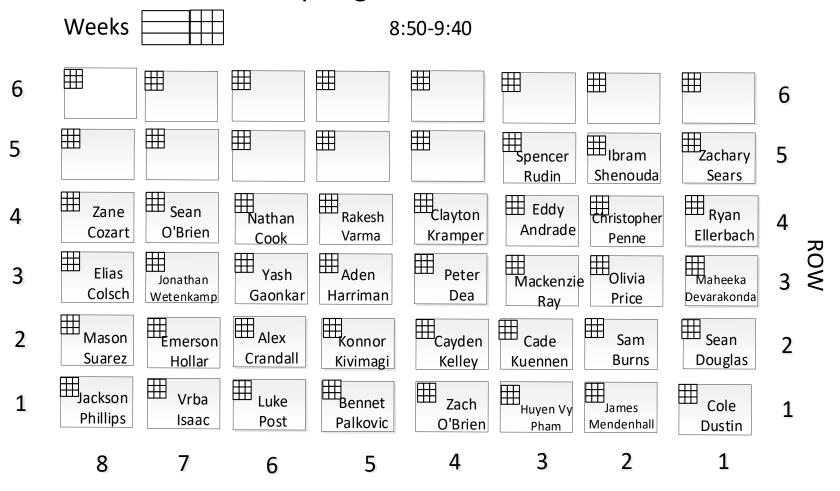

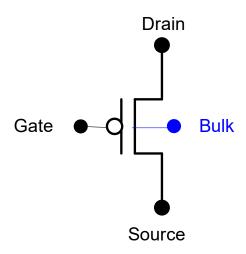

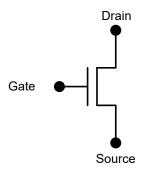

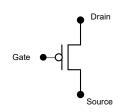

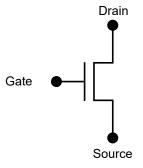

### **MOS** Transistor

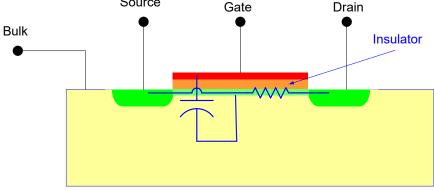

#### Qualitative Discussion of n-channel Operation

For V<sub>GS</sub> small

Gate Bulk

Source

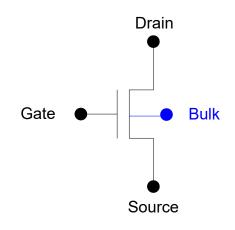

MOSFET actually 4-terminal device

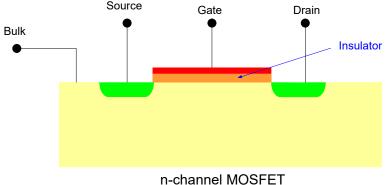

#### For V<sub>GS</sub> large

- Region under gate termed the "channel"

- When "resistor" is electrically created, region where it resides in channel is termed an "inversion region"

### **MOS** Transistor

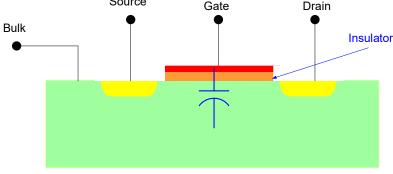

#### Qualitative Discussion of n-channel Operation

n-channel MOSFET

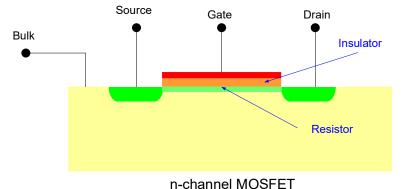

#### For V<sub>GS</sub> large

- Electrically created inversion layer forms a "thin "film" resistor

- Capacitance from gate to <a href="mailto:channel region">channel region</a> is distributed

- Lumped capacitance much easier to work with

### **MOS** Transistor

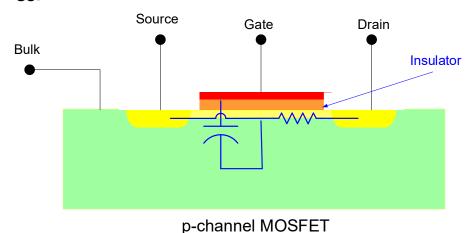

#### Qualitative Discussion of p-channel Operation

p-channel MOSFET

#### For |V<sub>GS</sub>| small

#### For |V<sub>GS</sub>| large

- Electrically created inversion layer forms a "thin "film" resistor

- Capacitance from gate to <u>channel region</u> is distributed

- Lumped capacitance much easier to work with

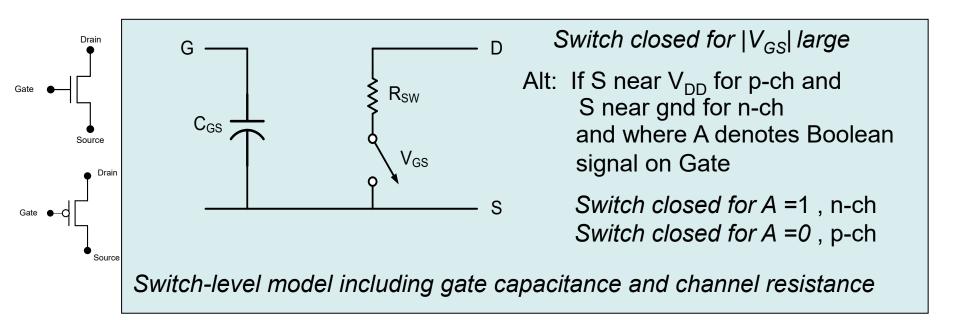

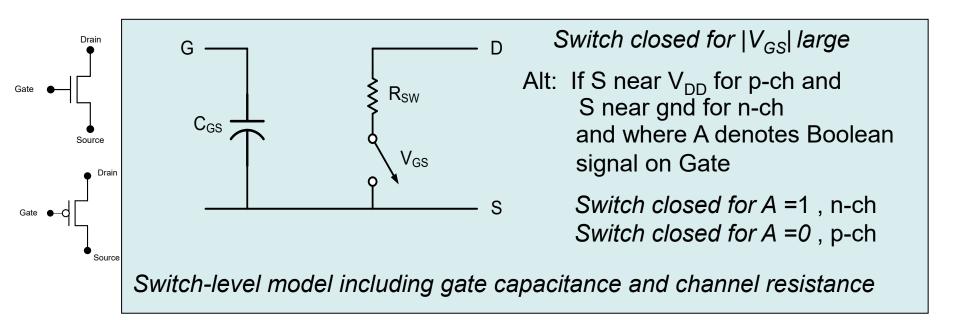

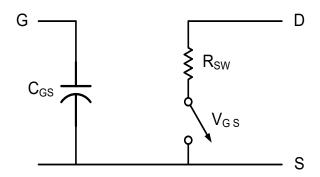

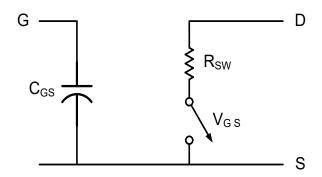

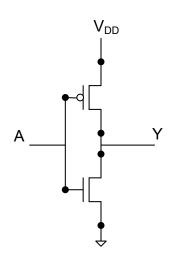

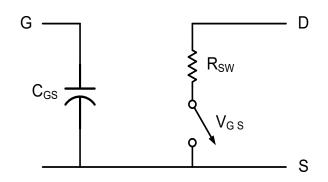

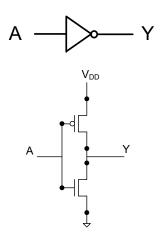

# Review from Last Time Improved Switch-Level Model

$C_{GS}$  and  $R_{SW}$  dependent upon device sizes and process

For minimum-sized devices in a 0.5 $\mu$  process with  $V_{DD}=5V$

$$C_{GS} \cong 1.5fF$$

$R_{sw} \cong \begin{bmatrix} 2K\Omega & n-channel \\ 6K\Omega & p-channel \end{bmatrix}$

Considerable emphasis will be placed upon device sizing to manage  $C_{GS}$  and  $R_{SW}$

# Review from Last Time Improved Switch-Level Model

$C_{GS}$  and  $R_{SW}$  dependent upon device sizes and process

Will assume for minimum-sized devices in a 0.18 $\mu$  process with  $V_{DD}=2V$

$$C_{GS} \cong 1.5fF$$

$R_{sw} \cong \begin{bmatrix} 2K\Omega & n-channel \\ 6K\Omega & p-channel \end{bmatrix}$

Considerable emphasis will be placed upon device sizing to manage  $C_{GS}$  and  $R_{SW}$

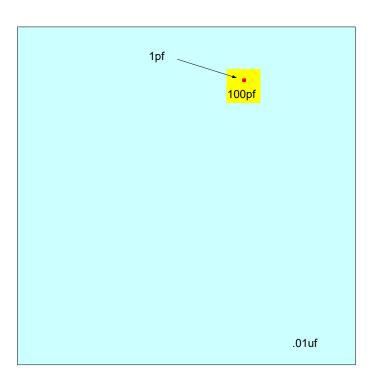

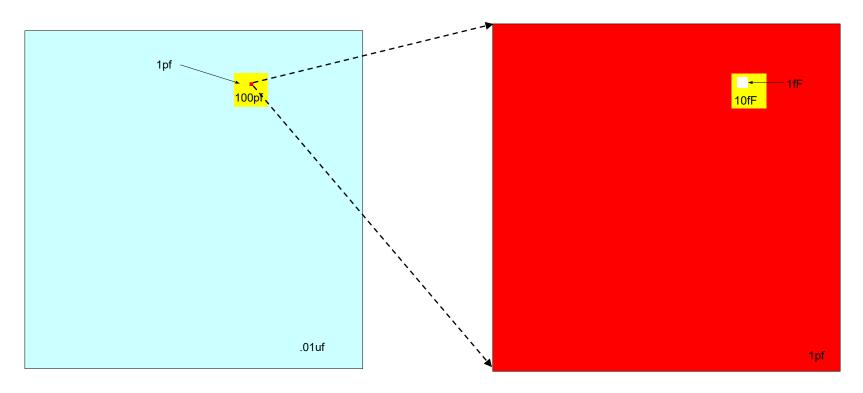

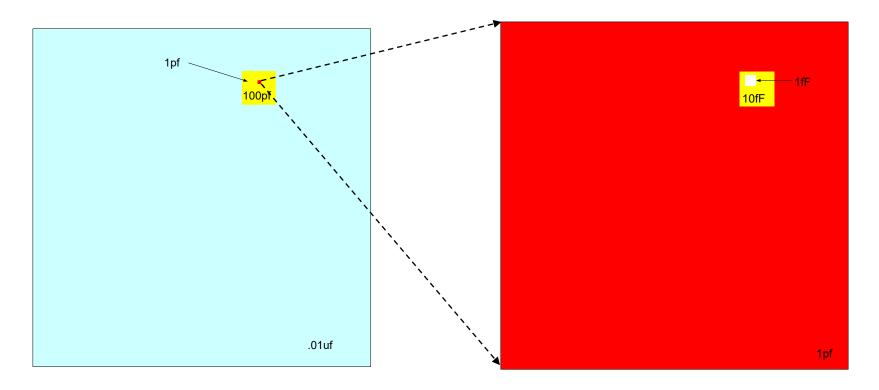

# Is a capacitor of 1.5fF small enough to be neglected?

From EE 201 Parts Kit

| Capacitor | s (Farads) |   |   |  |

|-----------|------------|---|---|--|

| 100p      |            | 3 |   |  |

| 470p      |            | 3 |   |  |

| 0.001u    |            | 3 | 2 |  |

| 0.0047u   |            | 3 | 2 |  |

| 0.01u     |            | 3 |   |  |

| 0.047u    |            | 3 |   |  |

| 0.1u      |            | 3 | 1 |  |

| 0.47u     |            | 3 |   |  |

| 1u        |            | 3 |   |  |

| 10u       |            | 3 |   |  |

| 100u      |            | 3 |   |  |

Area allocations shown to relative scale:

### Review from Last Time Is a capacitor of 1.5fF small enough to be neglected?

#### Area allocations shown to relative scale:

- Not enough information at this point to determine whether this very small capacitance can be neglected

- Will answer this important question later

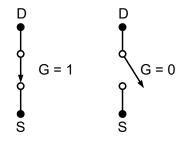

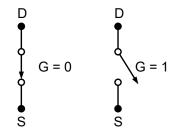

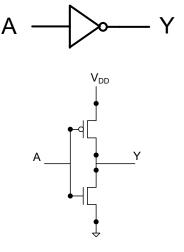

### Model Summary (for n-channel)

Switch-Level model

#### Improved switch-level model

Switch closed for  $V_{GS}$ = large Switch open for  $V_{GS}$ = small

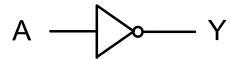

### Model Summary (for p-channel)

1. Switch-Level model

#### 2. Improved switch-level model

Switch closed for  $|V_{GS}|$  = large Switch open for  $|V_{GS}|$  = small

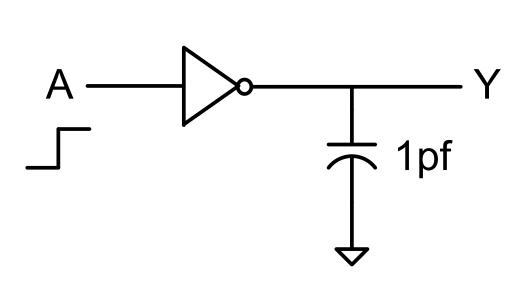

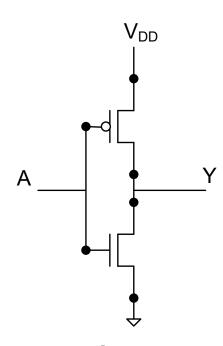

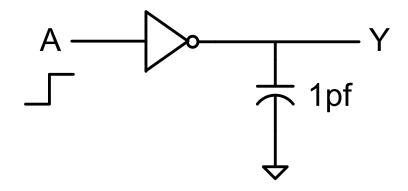

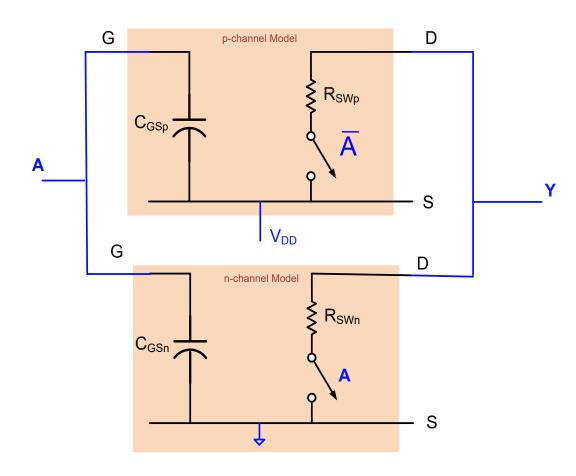

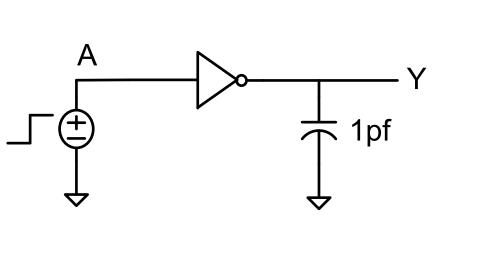

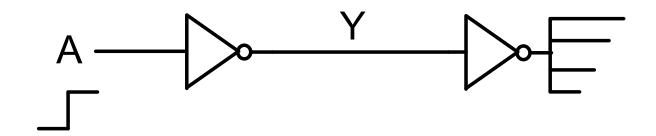

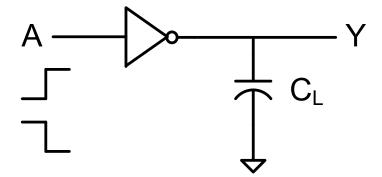

### **Propagation Delay**

### Example

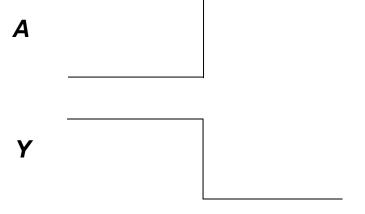

### What are $t_{HL}$ and $t_{LH}$ ?

#### Assume V<sub>DD</sub>=5V

With basic switch level model?

With improved switch level model?

Inverter

### Example

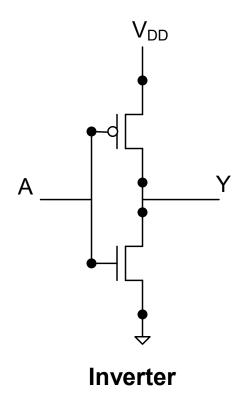

#### Inverter with basic switch-level model

### Example What are $t_{HL}$ and $t_{LH}$ at output?

Assume ideal step at A input

With basic switch level model

$$t_{HL}=t_{LH}=0$$

With simple switch-level model t<sub>HL</sub>=t<sub>LH</sub>=0

#### With improved model ?

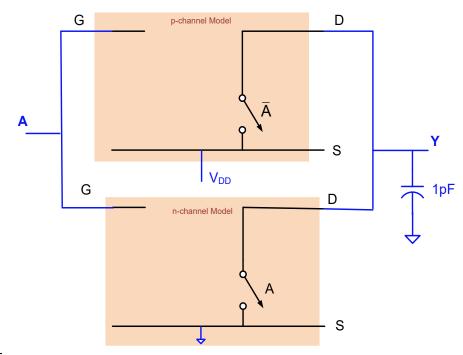

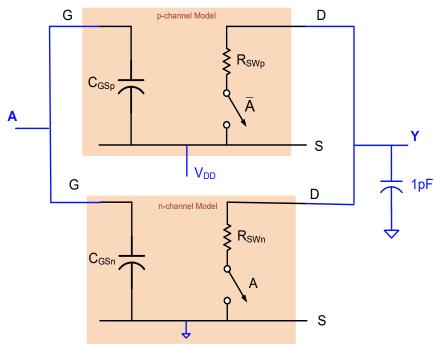

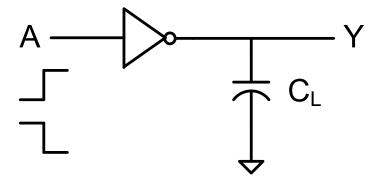

#### **Inverter Model?**

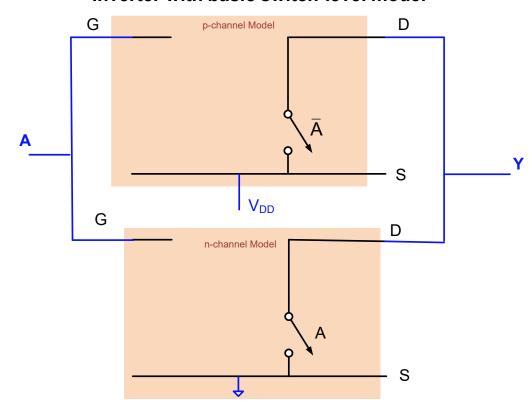

#### Inverter with improved model

#### **Inverter Model**

#### **Inverter with Improved Model**

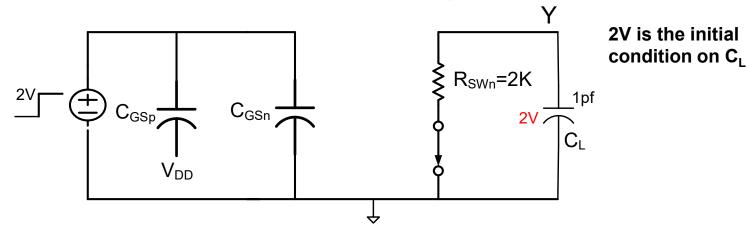

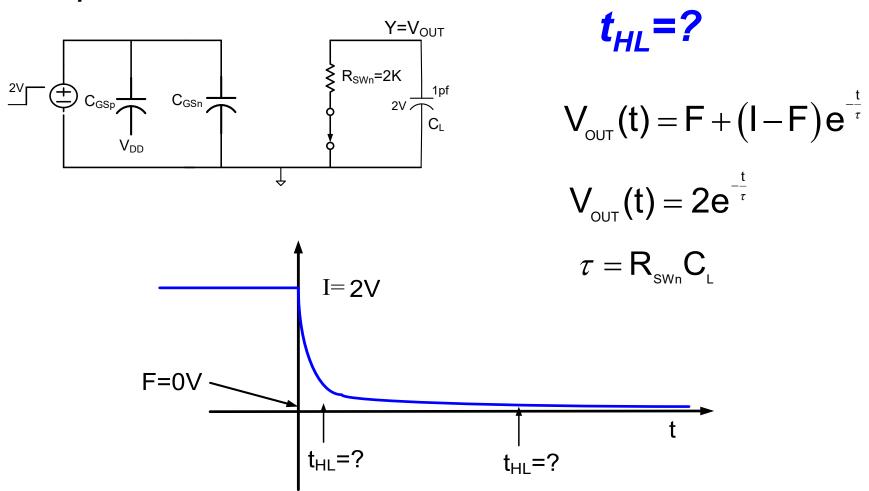

With improved model  $t_{HL}=?$

To initiate a HL output transition, assume Y has been in the high state for a long time, lower switch closes at time t=0, and upper switch opens just prior to t=0

#### With improved model

$$t_{HL}=?$$

Recognize circuit (specifically on right) as a first-order RC network

Recall: Step response of any first-order network with LHP pole can be written as

$$y(t) = F + (I - F)e^{-\frac{t}{\tau}}$$

where F is the final value, I is the initial value and  $\tau$  is the time constant of the circuit

(from Chapter 7 of Nilsson and Riedel)

For the circuit above, F=0, I=2 and  $\tau = R_{sw_0}C_1$

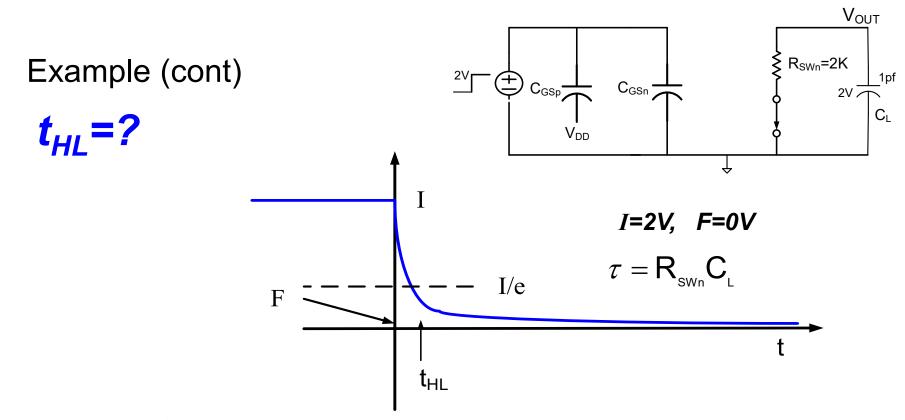

#### With improved model

how is t<sub>HL</sub> defined?

Define the time taken for output to drop to I/e

$$V_{\text{OUT}}(t) = F + (I - F)e^{-\frac{t}{\tau}} \qquad \longrightarrow \qquad \frac{I}{e} = F + (I - F)e^{-\frac{t_{\text{HL}}}{\tau}}$$

Is this simply a mathematical definition or does it have some practical significance?

$t_{HL}$  as defined here and as verified by experimental verification has proven useful at analytically predicting response time of circuits

#### With improved model

$$\frac{I}{e} = F + (I - F)e^{\frac{-t_{HL}}{\tau}}$$

$$\frac{I}{e} = Ie^{-\frac{t_{HL}}{\tau}}$$

$$\frac{1}{e} = e^{-\frac{t_{HL}}{\tau}}$$

$$t_{_{HL}}= au$$

$$t_{HL} = R_{swn} C_{l}$$

Both experimental results and accurate computer simulations show that this reasonably accurately predicts how quickly following stages recognize that a logic transition has taken place!!

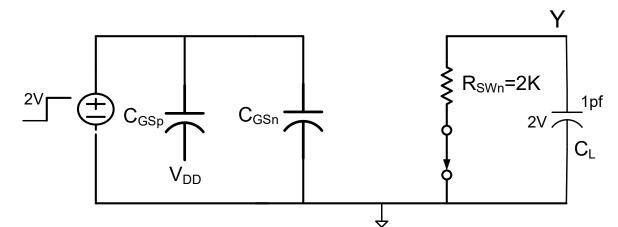

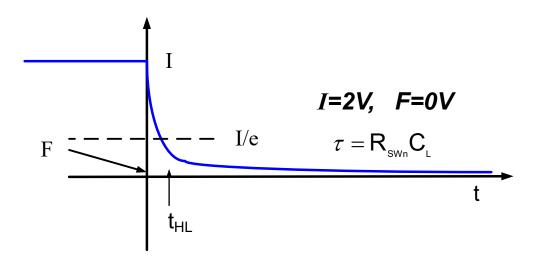

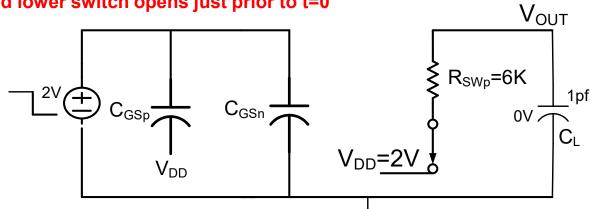

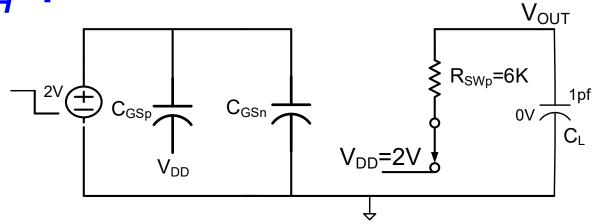

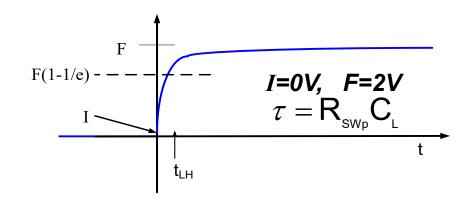

With improved model  $t_{IH}=?$

Assume output in low state for a long time and upper switch closes at time t=0 and lower switch opens just prior to t=0

**0V** is the initial condition on C<sub>L</sub>

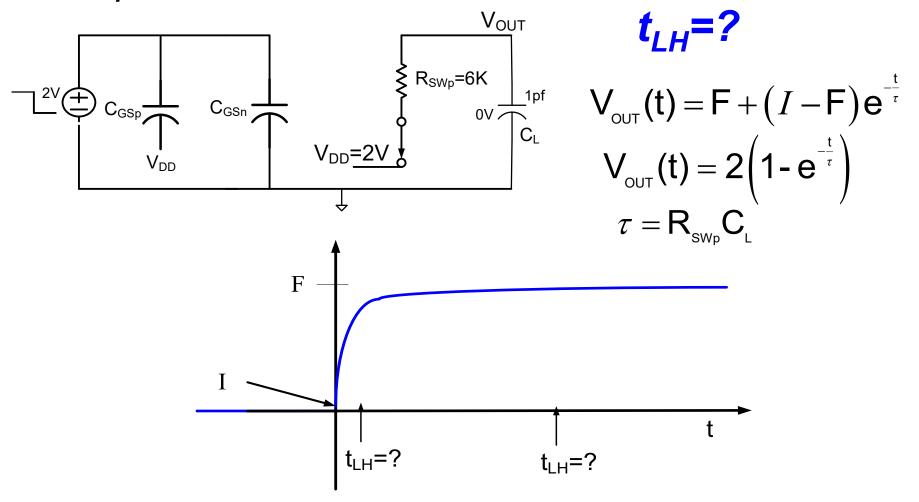

With improved model  $t_{LH}=?$

$$y(t) = F + (I - F)e^{-\frac{t}{\tau}}$$

For this circuit (specifically on the right), F=2, I=0 and  $\tau = R_{swp}C_L$

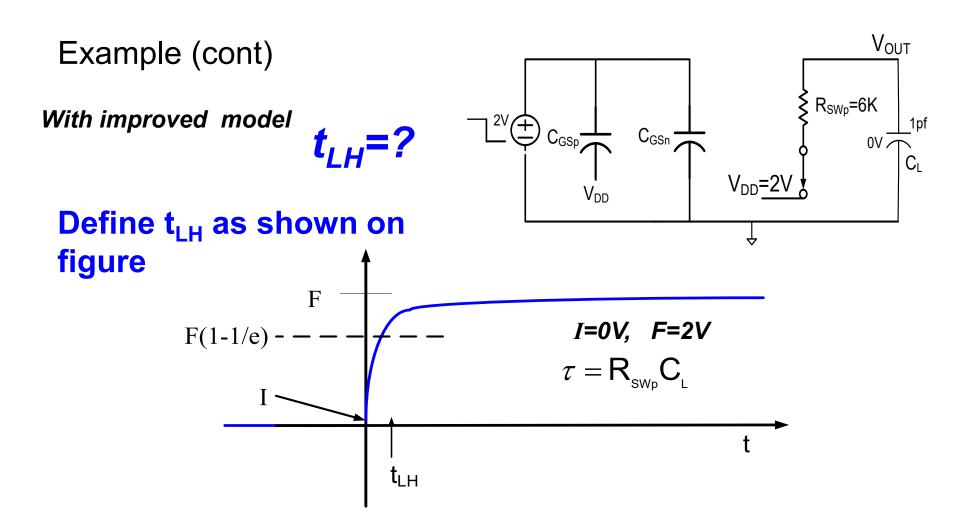

#### With improved model

how is t<sub>LH</sub> defined?

$t_{LH}$  as defined has proven useful for analytically predicting response time of circuits

$$V_{\text{OUT}}(t) = F + (I - F)e^{-\frac{t}{\tau}} \qquad \Longrightarrow \qquad F\left(1 - \frac{1}{e}\right) = F + (I - F)e^{-\frac{t_{\text{LH}}}{\tau}}$$

#### With improved model

$$t_{LH}=?$$

$$\mathsf{F}\left(1-\frac{1}{\mathsf{e}}\right) = \mathsf{F} + \left(I-\mathsf{F}\right)\mathsf{e}^{\frac{\mathsf{t}_{\mathsf{LH}}}{\tau}}$$

$$F\left(1-\frac{1}{e}\right) = F + (F)e^{\frac{-t_{LH}}{\tau}}$$

$$1 - \frac{1}{e} = 1 + e^{\frac{-t_{LH}}{\tau}}$$

$$t_{\perp} = \tau$$

$$t_{LH} = R_{SWp} C_{L}$$

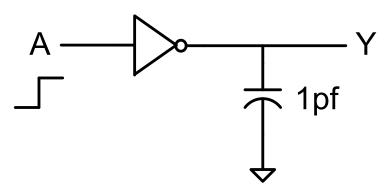

#### With improved model

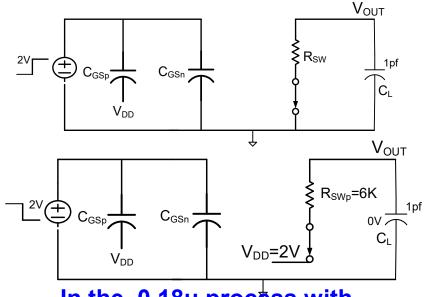

In the 0.18u process with minimum-sized devices

$$\mathbf{t}_{HL} \cong \mathbf{R}_{SWn} \mathbf{C}_{L} = 2K \cdot 1pF = 2n \sec t$$

$\mathbf{t}_{LH} \cong \mathbf{R}_{SWn} \mathbf{C}_{L} = 6K \cdot 1pF = 6n \sec t$

Note this circuit is quite fast!

Note that  $t_{HL}$  is much shorter than  $t_{LH}$

Often C<sub>L</sub> will be even smaller and the circuit will be much faster !!

Summary: What is the delay of a minimum-sized inverter driving a 1pF load?

$$\mathbf{t}_{\text{HL}} \cong \mathbf{R}_{\text{SWp}} \mathbf{C}_{\text{L}} \qquad = 6K \bullet 1pF = 6n \sec \mathbf{t}_{\text{LH}}$$

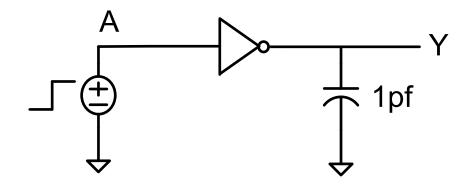

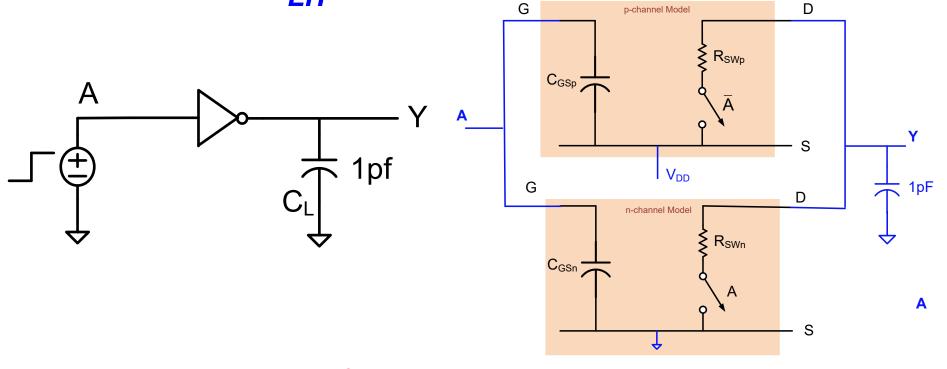

### Improved switch-level model

Switch closed for V<sub>GS</sub>= large

Switch open for  $V_{GS}$ = small

- Previous example showed why R<sub>SW</sub> in the model was important

- But of what use is the C<sub>GS</sub> which did not enter the previous calculations?

For minimum-sized devices in a 0.18µ process

$$C_{GS} \cong 1.5 fF$$

$R_{sw} \cong \begin{array}{c} 2K\Omega & n-channel \\ 6K\Omega & p-channel \end{array}$

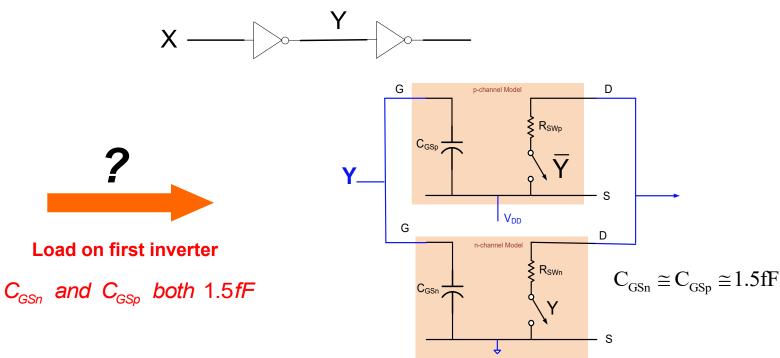

#### One gate often drives one or more other gates!

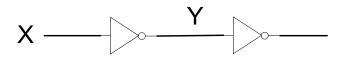

### What are $t_{HL}$ and $t_{LH}$ ?

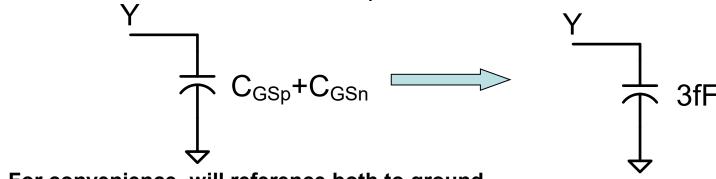

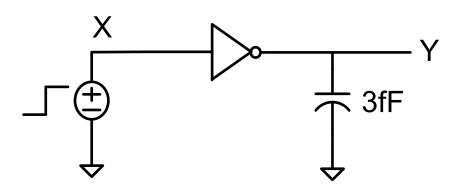

Example: What is the delay of a minimum-sized inverter driving another identical device?

Loading effects same whether  $C_{GSp}$  and/or  $C_{GSn}$  connected to  $V_{DD}$  or GND

For convenience, will reference both to ground

# Is a capacitor of 1.5fF small enough to be neglected?

Area allocations shown to relative scale:

This example will provide insight into the answer of the question

Example: What is the delay of a minimum-sized inverter driving another identical device? Assume  $V_{DD}$ =2V

Generalizing the Previous Analysis to Arbitrary Load

$$t_{HL} \cong R_{SWn}C_{L}$$

$t \simeq R C$

Example: What is the delay of a minimum-sized inverter driving another identical device?

$$\mathbf{x} \xrightarrow{\mathbf{Y}} \mathbf{Y}$$

$$\mathbf{T} \xrightarrow{\mathbf{X}} \mathbf{Y}$$

$$\mathbf{T}$$

Do gates really operate this fast?

What would be the maximum clock rate for acceptable operation?

Example: What is the delay of a minimum-sized inverter driving another identical device?

$$\mathbf{t}_{\text{HL}} \cong \mathbf{R}_{\text{SWp}} \mathbf{C}_{\text{L}} = 6p \sec \mathbf{t}_{\text{LH}}$$

$$\mathbf{t}_{\text{LH}} \cong \mathbf{R}_{\text{SWp}} \mathbf{C}_{\text{L}} = 18p \sec \mathbf{t}_{\text{SWp}} \mathbf{C}_{\text{L}}$$

What would be the maximum clock rate for acceptable operation?

$$T_{CLK-min} = t_{HL} + t_{LH}$$

$$f_{CLK-max} = \frac{1}{T_{CLK-min}} = \frac{1}{24psec} = 40GHz$$

And much faster in a finer feature process!! ??????

What would be the implications of allowing for 10 levels of logic and 10 loads (FanOut=10)?

Example: What is the delay of a minimum-sized inverter driving another identical device? SUMMARY

$$\mathbf{t}_{LH} \cong \mathbf{R}_{SWp} \mathbf{C}_{L} = 6K \bullet 3 fF = 18 p \sec \theta$$

This is very fast but even the small 1.5fF capacitors are not negligible!

These capacitors play a key role in determining the speed of a circuit!

#### Response time of logic gates

$$t_{_{HL}}\cong R_{_{SWn}}C_{_{L}}$$

$$t_{\scriptscriptstyle LH}\cong R_{\scriptscriptstyle SWp}C_{\scriptscriptstyle L}$$

- Logic Circuits can operate very fast

- Extremely small parasitic capacitances play key role in speed of a circuit

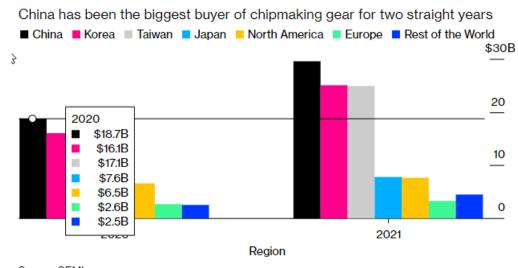

#### Some Observations about Technology and Politics

### Are the larger feature size technologies still used by industry today in the US or abroad?

GlobalData predicts that the <u>Chinese market will play a</u> <u>much smaller role for foreign suppliers by 2030</u>. More than 90% of the chips sold and used worldwide involve low-process production technology.

https://www.investmentmonitor.ai/analysis/china-lead-global-semiconductor-growth 2030#:~:text=Global %20semiconductor%20industry%20revolves%20around,Samsung 20Electronics%20and%20SK%20Hynix.

Source: SEMI

#### Some Observations about Technology and Politics

#### **Sept 2022**

https://technode.com/2021/03/04/where-china-is-investing-in-semiconductors-in-charts/

China is the world's largest consumer of semiconductors, and the lion's share of revenue from purchasing these chips go to foreign firms. China consumed \$143.4 billion worth of wafers in 2020, and just 5.9% of them were <u>produced</u> by companies headquartered in China.

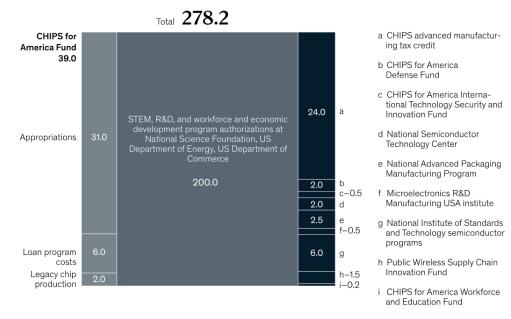

### The Chips Act of 2022

\$52 billion grant over five years to help grow the domestic semiconductor manufacturing. \$2 billion of which is to explicitly focus on legacy chip production. These chips are essential to the auto industry, the military, and other industries critical to our national security interests.

S

By the numbers: The CHIPS Act directs \$280 billion in spending over the next ten years. The majority-\$200 billion-is for scientific R&D and commercialization. Some \$52.7 billion is for semiconductor manufacturing, R&D, and workforce development, with another \$24 billion worth of tax credits for chip production. There is \$3 billion slated for programs aimed at leading-edge technology and wireless supply chains.

#### The CHIPS and Science Act of 2022 directs \$280 billion in spending over the next ten years, with the bulk for scientific R&D.

CHIPS and Science Act funding for 2022-26, \$ billion

Source: Creating Helpful Incentives to Produce Semiconductors (CHIPS) and Science Act of 2022, H.R. 4346, 117th Cong. (2022)

# How do I get CHIPS Act Funding?

Breaking News: The application for wafer manufacturers and suppliers of materials and equipment (e.g., chemicals and tools) was just released. Read the details here.

\$53 billion is available for semiconductor manufacturing and R&D, plus a 25% refundable tax credit for qualified CapEx.

See below to discover where your business fits in

Need help? Book an appointment with our professional grant writing team <a href="here">here</a> or email us: equity@chipsact.com

### Stay Safe and Stay Healthy!

### **End of Lecture 7**